Author: Florent Simonnot

Key features

+ emulates a 27C512 EPROM

+ file download via a serial port using three leads (Tx, Rx & GND) at a speed of 19,200 baud

+ compatible with Intel hex format

+ expansion connector for synchronisation with another emulator or system

+ CPLD programmable in AHDL using the MAXPLUS II BASELINE freeware development environment (or QUARTUS)

+ AVRGCC C compiler under GNU licence

More and more electronics hobbyists and professionals are using CPLDs to implement circuits. In this article, we work through the entire design process for a CPLD project from start to finish using a practical example. The result is a handy 27C512 EPROM emulator that is useful for debugging microcontroller systems.

This article shows you how to design an EPROM emulator with a minimum of ‘glue chips’. Various types of CPLD and FPGA devices have already been used in several projects published in Elektor Electronics, so many readers already know how easy it is to use these components to develop digital circuitry.

Altera EPM7064

We selected the EPM7064S EPLD from the Altera CPLD family for this project because it allows a handful of chips to be eliminated from the design. The separate buffers, bidirectional ports, multiplexers and latches that would normally be required are no longer necessary if a CPLD is used. That makes the circuit board layout considerably smaller and simpler. If you’ve been following our recent series of articles about CPLDs, you can now put your

knowledge to practical use with this project.

CPLD size

It’s a good idea to draft a list of the desired C PLD properties before selecting a particular device. On the one hand, there’s no point in purchasing an expensive CPLD if only ten percent of its capacity will be used, while on the other hand, if the selected CPLD is too small you will be forced to use every trick you know to squeeze the design into the available space. As every EPROM emulator must have a RAM capacity that is at least as large as that of the EPROM to be emulated, you already know several important parameters, particularly with regard to the required number of inputs and outputs (I/O pins). The calculation is straightforward: a 27C512 is organised as 64 KB × 8 bits, so you will need to have 16 address lines and 8 data lines available to emulate it. As the RAM in the emulator must have at least the same capacity, it will also require at least the same number of I/O lines. That gives a total of 48 I/O lines (16 × 2 + 8 × 2). If you add around ten control lines for enabling the tri-state

(high-impedance) mode and controlling other registers, you already end up with around 60 pins. It’s clear that a 44-pin or 64-pin package won’t meet your requirements, particularly if you consider that CPLDs generally require supply connections on all sides of the package and sometimes even require several different supply voltages, because the voltage required by the core logic (Vccint) is usually different from the voltage required by the I/O logic (Vccio). The net result in this case is that you’re looking at a PLCC84 package. It’s more difficult to estimate how much circuit capacity you will need. A good technique is to count the number of flip-flops you will need for functions such as registers and counters. For instance, if you want to implement a (rather) large counter composed of 40 JK flip-flops, a device such as the

EPM7032 is totally unsuitable because it has only 32 macrocells (as indicated by the type designation) that can be configured in the desired manner.

Counting registers

As can be seen from the block diagram in Figure 1, the microcontroller must perform its tasks using a link to the CPLD consisting of only 8 bits (from port A) and 3 control lines (from port C). Two sets of eight D-type flip-flops are needed to form a storage register for the 16 address bits of the RAM, and implementing this logic requires 16 macrocells. It must be possible to put the data bus in a high-impedance state in order to isolate the emulator from the target system, and that costs 8 macrocells in the CPLD. Another 16 single-bit multiplexers are needed to drive the data bus of the RAM, which receives its data from the target system or the D register – that’s another 16 cells. A total of 40 macrocells (16 + 8 + 16) are thus necessary, not including the control lines, which also require space in the peripheral interconnect matrix of the CPLD. An EPM70674S should be able to meet these requirements.

TDF vs. GDF

You might expect to see these letters on the rear of a sports car, but in this case they stand for ‘Text Design Files’ and ‘Graphic Design Files’. Although it would certainly be possible to describe the design using a sort of schematic diagram, here we use Altera’s native hardware description language (AHDL) instead, for two principal reasons...... (to be continued) Download PDF version for more details.

Simulation

Before programming the CPLD, you can test the design using a simulation (even though the design is quite simple). Start with creating a simulation file by clicking on File>New and selecting Waveform editor file. An empty page will be displayed, and the first thing you should do is to save it with the same name as the project (which is ‘emu’ in this case). The recommended method involves entering vectors based on the simulator netlist (.snf) file, which includes timing information for the design. The screen dump shown in Figure 5 should help clarifyall of this. ... (to be continued) Download PDF version for more details.

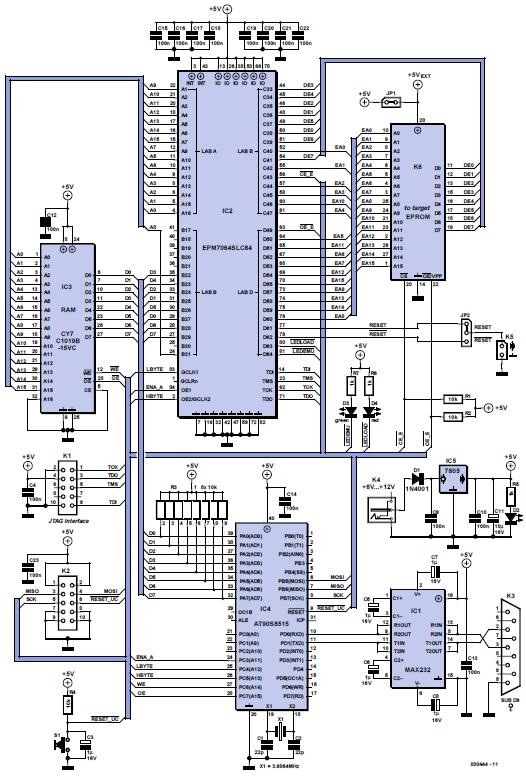

Figure 6. Despite the high pin counts of the principal components, the schematic diagram of the EPROM emulator is easy to understand.

Hardware

A glance at the schematic diagram in Figure 6 shows that it contains few secrets and closely matches the block diagram in Figure 1. Power is supplied by a mains adapter, but it can also be tapped off from the target system via the supply pins of the EPROM being emulated. In the latter case, you should verify that the quality of the available 5-V supply is adequate and fit a jumper at JP1. The sole purpose of diode D1 is to protect against a reverse polarity connection, which is always a possibility when you’re working on the bench. An interface IC in the form of a MAX232 (IC1) converts the RS232 signals to TTL levels. The microcontroller

(IC4) is an Atmel AT90S8515 with flash memory. It can be programmed in system via ISP connector K2, which feeds out the signal from the SP1 line and the reset signal. If you don’t want to program the microcontroller yourself, you can obtain a pre-programmed version from Readers Services (order number 030444-41). The board can be reset using a pushbutton switch in case of a crash. The CPLD (IC2) is connected to K1, which makes its JTAG signals available to the external world so it can be programmed using a suitable device. A pre-programmed version of this IC is also available (Readers Services ordernumber 030444-21). Note: in order to save space, the required resistors for the JTAG interface have been placed in the JTAG adapter cable. Also note the very large decoupling capacitors around the CPLD. They are necessary to ensure the quality of the supply voltage by absorbing current peaks that can cause EMI radiation. The RAM (IC3) has a capacity of 128 KB and a very short access time of only 15 ns, which is reason enough to use an SMD type.

The RAM sees all the busses connected to the Altera IC, but the control lines for writing data and enabling the outputs are driven by the microcontroller. The power supply requires little comment. An adapter with an output voltage in the range of 8–12 V can be used.

It is connected to K4. The 7805 regulator provides the 5-V supply voltage required by the emulator. LED D2 indicates that the supply voltage is present.

COMPONENTS LIST

| Resistors: | Capacitors: |

| Semiconductors: | Miscellaneous: |

![e05a038[7] e05a038[7]](https://blogger.googleusercontent.com/img/b/R29vZ2xl/AVvXsEie9MoN1cC1ErnPKjty0vhF8n756hqUNWVBO3S_YmoeYGrEnEFo14QDi5eF9y5dsQCaqObyQkuFII_T8qaES11FccAPusy6__ovH9QeTaaYZ2y2NuinapK7fND9UoWekKQcJd2B19v2ENov/?imgmax=800)

Figure 8. Fully assembled emulator prototype. It differs slightly from the final PCB supplied by us.

Note the especially small dimensions of some of the capacitors (including the 1-μF types).

Software

The program was written in C using the freeware GNU C compiler. That means that anyone who makes any changes to the program is obliged to disclose that fact and make the source code available... (to be continued) Download PDF version for more details.

Construction

Construction of the emulator is practically child’s play thanks to the doublesided, plated-through PCB, whose board layouts is shown in Figure 7. However, there are a few points that

require special attention. The SMD components used in the circuit must be fitted first. In particular, a fine-tipped soldering iron is required for the SMD capacitors on the solder side of the board (C12–C14) and the decoupling capacitors for the CPLD (C15-C22), and extra flux may be necessary. These components can be fitted quite easily. All it takes is a tiny bit of solder at each end. Resistors R1 and R2 are fitted under the DIP connector. Soldering the RAM (IC3) requires a certain amount of care. Start by placing it precisely on top of the solder

lands. Then solder two pins at the extreme corners. If the IC is properly positioned, you can continue with soldering the other pins, making sure to allow the IC enough time to cool down. It’s good practice to inspect the solder joints with a loupe after you’re finished. If there are any shorts between the pins, the excess solder can be removed using finely stranded wire with liquid flux...

....(to be continued) Download PDF version for more details.

Operation

The emulator communicates with the PC using Hyperterminal or a similar program. To initiate a dialogue, configure the program for a baud rate of 19,200, no handshake (neither hardware nor software), and ASCII-only dialogue. If the RS232 link is properly configured, the terminal window will display a welcome message after the supply voltage is switched on, along with a list of available instructions. To check whether everything is OK, you can make a simple test by pressing the ‘r’ key to read out the RAM. The content of the RAM will be arbitrary. Next, use the ‘c’ command to set the content of the RAM to ‘0x00’, and check this by reading out the RAM again. The ‘s’ key loads ‘0xFF’ into the memory. Type an ‘l’ on the PC to download a hex file and transfer it in text format. After the file has been loaded, you can type ‘e’ to read out the memory again and switch to emulation mode. You can reinitiate the process whenever you wish (such as after a crash or if the firmware detects an error in the transmitted data) by typing ‘R’. There is no timeout for entering commands or downloading hex files. That means you can also enter Intel hex code manually without any problems. Each CRC error or other error is indicated by an error message. You can easily transfer several files in succession to the emulator. They will be placed at the specified addresses without erasing or corrupting the data already present. It is also possible to make changes manually. Than can be handy when you want to modify a few values without recompiling and downloading the entire program.

Final remarks

This is clearly a project that can be modified according to your particular ideas and wishes.

It is an ‘open’ project in the sense that all of the source code is freely available from the moment that it is published, in accordance with the conditions of the GNU licence.

References: ‘EPROM Emulator’, Elektor Electronics, November 2002

Internet

Version 10.2 of MAX+PLUS II:

www.altera.com/products/software/products/legacy/max/sof-emax_baseline.html

Version 4.2 of QUARTUS II (several dozen MB!):

www.altera.com/support/software/download/altera_design/quartus_we/dnl-quartus_we.jsp

Migrating from MAX+PLUS II to QUARTUS II:

www.altera.com/products/software/switching/maxplus2/qts-mp2_user.html

All about the MAX 7000 family:

www.altera.com/products/devices/max7k/m7k-index.html

MAX 7000 datasheet: www.altera.com/literature/ds/m7000.pdf

CYC1019B datasheet:

www.cypress-japan.co.jp/products/datasheet.php?partnum=CY7C1019B&familyid=36

GNU compiler, a large number of links to private Internet sites for SPI programmers,

and a fantastic forum: www.avrfreaks.org

(Elektor Electronics Magazine - 10/2005)

|  030444-11.zip (>>or SkyDrive link) 030444-11.zip (>>or SkyDrive link) Download this article #e05a038.pdf >>or SkyDrive link. Download PCB layout #030444-PCB.pdf >>or SkyDrive link. |

Labels

- * Elektor 2005 (9)

- * Elektor 2006 (72)

- Adapters (1)

- ADC / DAC (1)

- AM / FM (2)

- Amplifiers (3)

- Antennae (2)

- Articles List (1)

- Audio (1)

- Automatic (2)

- Batteries (3)

- Bluetooth (1)

- Breakers / Contacts (1)

- Buzzers / Sirens (1)

- Clocks / Timers (2)

- Computer (2)

- Converters (2)

- Coolers / Fans (1)

- Counters (1)

- Datasheets (7)

- E-blocks (1)

- Energy (2)

- Flash / Light (8)

- Frequency (1)

- Fuse (1)

- Generators (2)

- High-voltage (1)

- Indicators (2)

- Infrared (IR) (4)

- LCDs (1)

- LEDs (7)

- Magazines (1)

- Meters (5)

- Microcontroller (9)

- Mobile Phone (1)

- Motors (1)

- OPAMP (3)

- PCB (1)

- Photosensors (1)

- Power Supply (2)

- Preamplifiers (1)

- Programming (3)

- Radio (1)

- Rectifiers (1)

- Regulators (1)

- Relays / Switches (10)

- Remote Control (7)

- RS232 (3)

- Security (4)

- Sensors (2)

- Servo (2)

- Simulators (1)

- Small Circuits (46)

- Telephones (2)

- TENS (1)

- Testers (3)

- Timebase (1)

- Tools (1)

- Transmitters (1)

- Trigger (1)

- USB (2)

0 comments: